previous

| contents | next

584 Part3½ Computer Classes

Section 1½ Monolithic Microcomputers

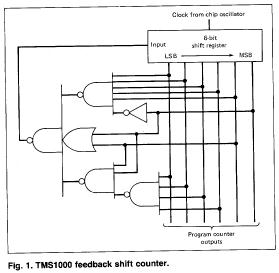

architecture with the largest installed base. The internal clock rate

varies from 200 to 450 KHz, depending on technology.

A follow-on to the TMS1000 is the TMS7000 series announced in 1981 [Hayn,

McDonogh, and Bellay, 1981]. The TMS7000 is an 8-bit monolithic microcomputer

with 2 or 4 Kbyte a user-definable instruction set. The first two chips,

the 7020 and 7040, have 2 or 4 Kbyte of use ROM respectively, and 128 bytes

of RAM in a 40-pin package. Up to 60 Kbyte of external memory can be added.

A complete family of monolithic microcomputers is planned.

PIC1650

In 1978, General Instrument Corporation (GI) introduced a single-chip

computer called the PIC 1650 (Programmable Intelligent Controller). Five

variations have been produced varying in number of pins (18 to 40), amount

of ROM (256 to 1,024 twelve-bit words), amount of RAM (24 to 64 eight-bit

bytes), and operational voltage range. The large majority (67 to 80 percent)

of the pins are devoted to program-controlled I/O.

GI sought an easy-to-program, general-purpose microcontroller. Thus

the PIC1650 differs from the TMS1000 in several significant areas:

-

Fixed rather than user-PLA-defined instruction set. In order to increase

instruction-set power, symmetry, and understandability, the PLC instruction

word was specified to be larger than the internal data path (i.e., 12 bits

as opposed to 8 bits). This is in direct contrast to the more conventional

practice of making instruction and data words of equal length.

-

Focus on 8-bit integer and boolean data-types rather than a 4-bit BCD data-type.

Typical control applications are better suited to 8-bit integer data-types

for sensing and controlling the magnitude of variables and to boolean data-types

for sensing and controlling on/off conditions.

-

Program-controlled rather than PLA-controlled output codes. A special literal

output instruction allows users to define code conversion tables in memory,

adding to display flexibility and variety.

Adherence to the single-word instruction format (which simplifies the implementation

of the 1650) poses serious problems for expansion when technology allows

more ROM to be implemented on a chip and control applications require more

than the 256 to 1,024 words of program in the current PIC architecture.

The small-address-space problem has been encountered in all classes of

computers; hence there is a wide range of solutions that have historically

been tried. The following is a list ordered from smallest to greatest impact

on existing user code:

-

Increasing the instruction word width by adding more bits to the address

field.

-

Bank registers: one or more registers, loadable by a special instruction,

that are concatenated with the program counter. The user must explicitly

manage addressability and he concerned about the absolute value of addresses

for various code segments. This scheme has been used in the PDP-8 and Data

General Nova minicomputers.

-

Address translation: a set of address translation registers placed between

the Pc and Mp. The registers supply more bits of physical address than

are contained in the instruction word. This scheme has been used in several

minicomputers, such as the PDP-11.

-

Addressing modes: Adding new addressing modes to the ISP that combine the

contents of new, wider, architecture registers with the address supplied

by the instruction. An example of this is the base/displacement addressing

in the IBM System/360-System/370.

The PIC 1650 has been used in electronic toys (by Ideal Toy and Coleco),

electronic scales (Detecto), and cameras (Bosch).

previous

| contents | next