Very Rave

Copy of

Corson Bell

CDC 8600

BARC, SLITE 830

Manuel

361 Howard Striet

SM FRANCISCE CA 94105-2241

USA

Gordon, Herewith

8600 Ry Man (Prel) US Paters 3833889

Rob Poller

| Job Co | ode Sheet Title           |                 |         |          | s                              | Y        | D           | ٨                                      | C      | 3      |

|--------|---------------------------|-----------------|---------|----------|--------------------------------|----------|-------------|----------------------------------------|--------|--------|

|        |                           |                 |         | Т        | Sheet                          | Ref.     |             |                                        | Α      | 4      |

| ł      |                           |                 |         |          | <u> </u>                       |          |             |                                        |        | _      |

|        |                           |                 |         |          | © SYE                          | to the n | naterial co | ontained                               | in thi | s      |

|        |                           |                 |         | <u></u>  | docume<br>be repro<br>by any m | duced or | transmit    | ted in an                              | y form | n, or  |

| legue  | Changes Since I set Issue | Originator Date | Checked | Approved | of SYDA                        | C Ptv Lt | d.          | ······································ |        | ,,,,,, |

8600

COMPUTER

SYSTEM

8600 RS. Manual

CONTROL DATA CORPORATION

CHIPPEWA LABORATORY

```

CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION *

ONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION *

NTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * C

TROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CH

ROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHI

OL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIP

L DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPP

DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPE

DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEW

ATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA

TA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA

A CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA L

CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA LA

CORPORATION * C

* CHIPPEWA LAB

ORPORATION * CH

CHIPPEWA LABO

RPORATION * CHI

CHIPPEWA LABOR

PORATION * CHIP

HIPPEWA LABORA

ORATION * CHIPP

PRELIMINARY

IPPEWA LABORAT

RATION * CHIPPE

PPEWA LABORATO

ATION * CHIPPEW

8500

PEWA LABORATOR

TION * CHIPPEWA

EWA LABORATORY

ION * CHIPPEWA

MANUAL

REFERENCE

WA LABORATORY

ON * CHIPPEWA L

A LABORATORY *

N * CHIPPEWA LA

LABORATORY *

* CHIPPEWA LAR

LABORATORY * C

* CHIPPEWA LABO

ABORATORY * CO

CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CON

CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONT

HIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTR

IPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL

PPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL

PEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL

EWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL D

WA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DA

A LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DAT

LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA

LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA

ABORATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA C

BORATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CO

ORATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA COR

RATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORP

ATORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPO

TORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPOR

ORY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORA

RY * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORAT

Y * CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATI

* CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATIO

* CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION

CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION

CONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION *

ONTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION *

NTROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * C

TROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CH

ROL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHI

OL DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIP

L DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPP

DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPE

DATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEW

ATA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA

TA CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA

A CORPORATION * CHIPPEWA LABORATORY * CONTROL DATA CORPORATION * CHIPPEWA L

```

CORPORATION \* CHIPPEWA LABORATORY \* CONTROL DATA CORPORATION \* CHIPPEWA LA

SPECIAL COPY FOR CANADIAN DIV.

PRELIMINARY

8500

REFERENCE MANUAL

This is an incomplete working draft and will be enlarged, corrected and revised periodically. Distribution is restricted to those listed below.

#### Distribution:

- L. W. Gallup

- R. C. Moore

- T. A. Ammerman

- D. W. Swedberg

- D. A. Canlander

- M. C. Willis

- P. G. Juetten

- G. Mc Crossen

- R. W. Sauls

- D. G. Grina

- W. L. Bhend

- R. A. Horton

- J. B. Pearson

- W. C. Katz

- G. A. Simpson

44 07 72

## Table of Contents

|       | Part | 1     | 8000 Instruction Formats and Codes                                                                                                                                                                                                                               | 1-1                                                                       |

|-------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|       | Part | 2     | System Description                                                                                                                                                                                                                                               |                                                                           |

|       |      |       | Introduction<br>8000 Processor                                                                                                                                                                                                                                   | 2-1                                                                       |

|       |      |       | Instruction word stack &         instruction address stack modules         Register modules         Floating add modules         Floating multiply modules  Memory I/O Section Exchange packages I/O channel request Floating point arithmetic Binary arithmetic | 2-3<br>2-6<br>2-9<br>2-10<br>2-11<br>2-15<br>2-16<br>2-18<br>2-19<br>2-20 |

|       | Part | 3     | Instruction Descriptions                                                                                                                                                                                                                                         | 3-1                                                                       |

| Apper | ndix |       |                                                                                                                                                                                                                                                                  |                                                                           |

|       | А    | Index |                                                                                                                                                                                                                                                                  | A - 1                                                                     |

|       | 8    | Di-bi | t/octal/decimal/hexadecimal table                                                                                                                                                                                                                                | B <b>- 1</b>                                                              |

## Part 1 8000 INSTRUCTION FORMATS & CODES

#### INSTRUCTION FORMATS

4-bit instruction codes (1 or 2 parcels)

F i ] k

[ | | | | ]

[ 4 | 4 | 4 | 4 ]

[ | | | ]

F = Instruction code

K = 20 bit constant

6-bit instruction codes (1 parcel)

F n J n

[ | | | | ]

[ 6 | | | | | 4 | ]

[ | | | | | ]

F = Instruction code

n = 6-bit constant

j = X register designator

for operand source

8-bit instruction codes (1 or 2 parcels)

F J k

[ | | 1 | 3

[ 8 | 4 | 4 ]

[ | | 1 | 3

F = Instruction code

K = 20-bit program constant

### 8000 INSTRUCTION CODES

| dibits/ | hex. |                                                      | clock<br>periods |

|---------|------|------------------------------------------------------|------------------|

| 0000    | 0 0  | Program error exit                                   |                  |

| 0001    | 01   | Logical product of (X)) and (Xk) to X)               | 2                |

| 0002    | 02   | Logical sum of (X)) plus (Xk) to X)                  | 2                |

| 0003    | 03   | Logical difference of (X]) minus (Xk) to X]          | 2                |

|         |      |                                                      |                  |

| 0010    | 04   | Copy (Xk) to Xj                                      | 2                |

| 0011    | 05   | Copy complement of (Xk) to Xj                        | 2                |

| 0012    | 06   | Shift (X)) left by (Xk) or right if (Xk) is negative | 3                |

| 0013    | 07   | Shift (X)) right by (Xk) or left if (Xk) is negative | 3                |

|         |      |                                                      |                  |

| 0020    | 8 0  | Floating DP sum of (Xj) plus (Xk) to Xj              | 8                |

| 0021    | 09   | Floating DP difference of (X)) minus (Xk) to X)      | 8                |

| 0022    | 0 A  | Floating divide of (X]) by (Xk) to X]                | 32               |

| 0023    | 0 B  | Population count of $(X_K)$ to $X_j$                 | 5                |

|         |      |                                                      |                  |

| 0030    | 0 C  | Floating DP product of (X)) times (Xk) to X)         | 8/3              |

| 0031    | 0 D  | Integer product of (XJ) times (Xk) to XJ             | 8/3              |

| 0032    | 0 E  | Program error exit                                   |                  |

| 0033    | 0 F  | Pass                                                 | 1                |

| dibits/ | hex.       |                                                      | clock<br>periods |

|---------|------------|------------------------------------------------------|------------------|

| 0100    | 10         | Transmit k to Xj                                     | 2                |

| 0101    | 11         | Transmit complement k to Xj                          | 2                |

| 0102    | 12         | Integer sum of (X)) plus k to X)                     | 3                |

| 0103    | 13         | Integer difference of (X)) minus k to X)             | 3                |

|         |            |                                                      |                  |

| 0110    | 14         | Unpack coefficient of (X)) to Xk                     | 2                |

| 0111    | 15         | Unpack exponent of (X)) to Xk                        | 2                |

| 0112    | 16         | Pack coefficient Xk and exponent X] to Xk            | 2                |

| 0113    | 17         | Integer difference 0 - (Xk) to Xj                    | 3                |

|         |            |                                                      |                  |

| 0120    | 18         | Begin system call [MTF]                              | . 1              |

| 0121    | 19         | End system call [MTF]                                | 1                |

| 0122    | 1 A        | Block read input channel (X) to address (XK) [MTF]   |                  |

| 0123    | <b>1</b> B | Block write output channel (X)) from addr.(Xk) [MTF] |                  |

|         |            |                                                      |                  |

| 0130    | 1 C        | Read channel request to XJ [MTF]                     | 4                |

| 0131    | 10         | Enter XA from Xk [MTF]                               | 1                |

| 0132    | 1 E        | Program error exit                                   |                  |

| 0.133   | 1 F        | Program error exit                                   |                  |

| dibits/ | hex. |                                                         | clock<br>periods |

|---------|------|---------------------------------------------------------|------------------|

| 0200    | 20   | Store (X)) data into memory at address K                | 1                |

| 0201    | 21   | Store (X)) data into memory at address (Xk)             | 1                |

| 0202    | 22   | Read/store: data at addr. K to X] / (X]) to addr. K     | 15+              |

| 0203    | 23   | Read/store: data at addr.(Xk) to X) / (X)) to addr.(Xk) | 15+              |

|         |      |                                                         |                  |

| 0210    | 24   | Read data at address K to X)                            | 15+              |

| 0211    | 25   | Read data at address (Xk) to X)                         | 15+              |

| 0212    | 26   | Read program at absolute address K to Xj                | 15+              |

| 0213    | 27   | Read program at absolute address (Xk) to Xj             | 15+              |

|         |      |                                                         |                  |

| 0220    | 28   | Read program at absolute address P + K to XJ            | 15+              |

| 0221    | 29   | Transmit P + K to Xj                                    | 3                |

| 0222    | 2 A  | Transmit K to X)                                        | 2                |

| 0223    | 2B   | Transmit XA to XJ                                       | 2                |

|         |      |                                                         |                  |

| 0230    | 2 C  | Set Interlock flags from Xk (IPF)                       | 1                |

| 0231    | 2 D  | Clear interlock flags from Xk (IPF)                     | 1                |

| 0232    | 2E   | Read interlock register to XJ                           | 2                |

| 0233    | 2F   | Read internal clock to XJ                               | 2                |

| dibits | /hex.      |                                                       | clock<br>periods |

|--------|------------|-------------------------------------------------------|------------------|

| 0300   | 3 0        | Jump to P + K                                         | 7-18+            |

| 0301   | 31         | Set (X)) = P and call subroutine at P + K             | 7-18+            |

| 0302   | 32         | Jump to P + K if (X)) in range                        | 3-7-18+          |

| 0303   | 33         | Jump to P + K if (X)) not in range                    | 3-7-18+          |

|        |            |                                                       |                  |

| 0310   | 34         | Jump to P + K if (X)) is equal to zero                | 3-7-18+          |

| 0311   | 35         | Jump to P + K if (X)) is not equal to zero            | 3-7-18+          |

| 0312   | 36         | Jump to P + K if (X)) is positive                     | 3-7-18+          |

| 0313   | 37         | Jump to P + K if (X)) is negative                     | 3-7-18+          |

|        |            |                                                       |                  |

| 0320   | 38         | Set (X)) = P and call subroutine at K                 | 7-18+            |

| 0321   | 39         | Set (X)) = P and call subroutine at (Xk)              | 7-18+            |

| 0322   | 3 A        | Set (X)) = P & call lip. routine at addr. K [clear PR | Fl 18+           |

| 0323   | 3B         | Set (X)) = P & call lib. rout. at addr.(Xk) [clear PR | F] 18+           |

|        |            |                                                       |                  |

| 0330   |            | Subroutine exit to (X)) + k                           | 7-18+            |

| 0331   |            | Library exit to (Xj) + k [set/clear PRF]              | 18+              |

| 0332   | <b>3</b> E | Jump to K                                             | 7-18+            |

| 0333   | 3F         | Exchange exit                                         |                  |

| dibits        | /hex•      |                                              | clock<br>periods |

|---------------|------------|----------------------------------------------|------------------|

| 100X          | 40         | Save lower (X1) for n bits                   | 2                |

| 101X          | 44         | Blank lower (XJ) for n bits                  | 2                |

| 102X          | 48         | Left shift (X)) by n bits                    | 3                |

| 103X          | 4 C        | Right shift (X)) by n bits                   | 3                |

|               |            |                                              |                  |

| 11XX          | 5 x        | Integer sum of (X)) plus K to Xi             | 3                |

| 12XX          | 6×         | Integer sum of (X)) plus (Xk) to Xi          | 3                |

| 1 3 X X       | 7 x        | Integer difference of (XJ) minus (Xk) to Xi  | 3                |

|               |            |                                              |                  |

| 2 0 X X       | 8 <b>x</b> | Floating sum of (XJ) plus (Xk) to Xi         | 8                |

| 21XX          | 9 <b>x</b> | Floating difference of (X)) minus (Xk) to Xi | 8                |

| 22 <b>X</b> X | A×         | Floating product of (X)) times (Xk) to Xi    | 8/3              |

| 23XX          | Вх         | Branch backward i words if (X)) < (Xk)       | 3-7-18+          |

|               |            |                                              |                  |

| 3 0 X X       | C×         | Read data at address (XJ) + K to Xi          | 15+              |

| 31XX          | Dχ         | Read data at address (X)) + Xk to Xi         | 15+              |

| 32XX          | Ε×         | Store data at address (X)) + K from Xi       | 1                |

| 33XX          | Fx         | Store data at address (XJ) + (Xk) from Xi    | 1                |

# Part 2 SYSTEM DESCRIPTION

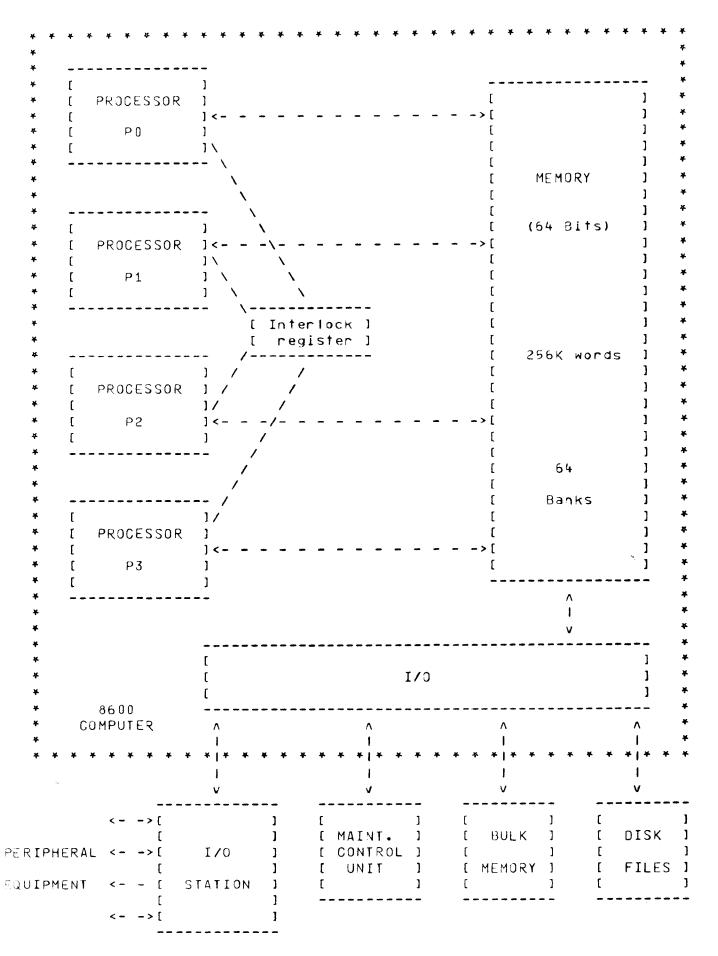

Fig. 2-1 8600 SYSTEM

#### INTRODUCTION

The 8600 system is a multi-processor system with four 8000 processors sharing a common 256K 64-bit word memory (figure 2-1). The processors communicate with an I/O station, maintenance control unit (MCU), bulk memory, and disk files through the common memory via sixteen independent I/O channels. The I/O station (typically a 6000 station configuration or a 7000 I/O station) handles all I/O operations.

Each of the four 8000 processors is an independent computation unit including arithmetic units, sixteen 64-bit operating registers, and a twelve word instruction stack (figure 2-2). Part 1 of this manual lists the instruction repertoire for the 8000 processors, and Part 3 provides descriptive information for each instruction. Each processor executes programs or program segments stored in the common memory upon command or assignment by the operating system software or programs operating under the control of the operating system. The 8600 operating system software will be described in a separate manual.

#### 8600 System Parameters

8000 Processor Unit (13 modules)

- 64-bit internal word

- binary computation in fixed point and floating point format

- twelve word instruction stack

- synchronous internal logic with 8 nanosecond clock period (clock frequency variable in 5% increments by MCU program)

#### Memory (66 modules)

- 256K words of linear select memory (64-bit words)

- 64 independent banks

- 4096 words per bank

- 250? nanosecond read/write cycle time

- 8 nanosecond per word maximum transfer rate

#### I/O Section (8 modules)

- 16 channels

- each channel full duplex

- 40? nanosecond per 64-bit word maximum transfer rate

The 8600 system is the result of a development program to provide computing capacity substantially beyond that of the 7600 systems. By using the multi-processing capabilities of the 8600, computation in the 8600 is expected to average ten times as fast as corresponding computation in the 7600 system. The 8600 is not machine code compatible with 7600 systems.

The 8600 is physically packaged in 125 pluggable modules (6" x 8" x 2.5"). There are 13 modules in each of the four 8000 processors, 66 modules in the memory, and 8 I/O modules. In the manual sections which follow, the system operation will be described in terms of module functions when practicable.

```

* Normalize

[ ]

---[ FLOATING ]

[ [ MULTIPLY ]

---[ [ MODULES ]

[ [ [ MA ]

* Floating divide

* Initial shift

* Population count

[ ]

---[ FLOATING ]

[ [ DIVIDE ]

[ [ MODULES ]

---[ FLOATING ]

[ [ ADD ]

[ [ MODULES ]

[ [ FA ]

[ -----

[ [ MB ]

[ DA ]

i FB 1

1

1

1

1

6

[ ] * 16 X registers

---[ REGISTER ] * Shift

[ [ MODULES ] * Boolean

---[ [ bits ] * Mask

[ [ RA 0-15 ] * Pack/Unpack

---[ [ ----- * Long add

[ [ RB 16-31 ] * XPW register

[ ------see

[ RD 48-63 ] Fig.

```

```

[ INSTR. ]

[ WORD ] see

MEMORY - -64- ->[ STACK ] Figs. MEMORY<- 20 - ->[ STACK ] Fig.

[ MODULE ] 2-4,5 SA [ MODULE ] 2-4

[ IW ]

* 12 word IWS

* RA adder

* P register

* P register

* IPT register

```

Fig. 2-2 8000 PROCESSOR

#### 8000 PROCESSOR

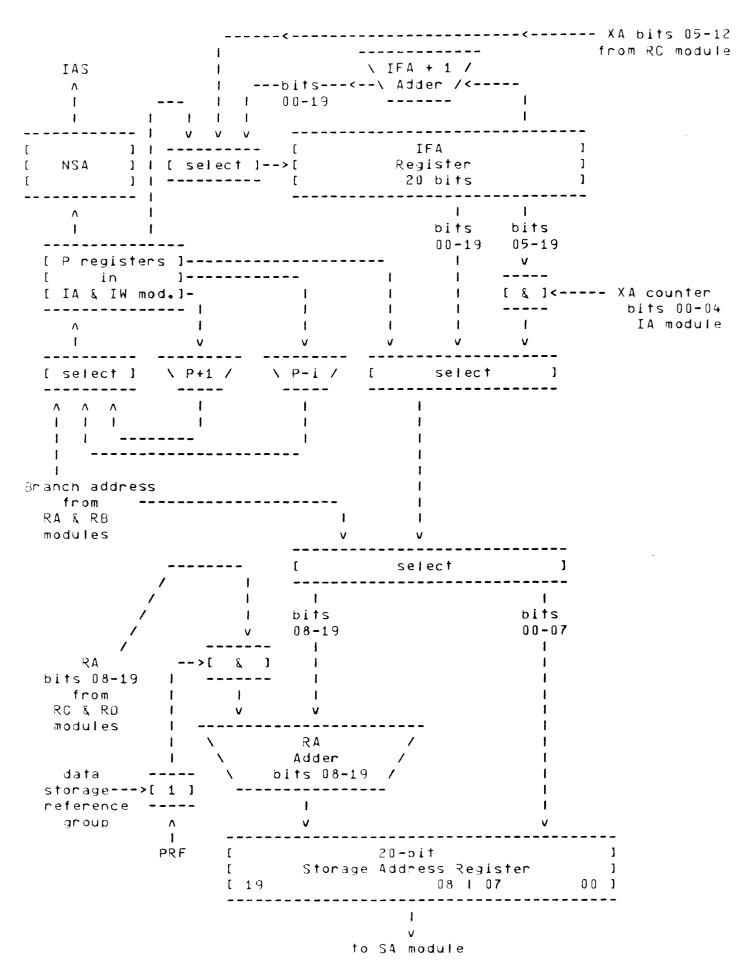

Instruction Word Stack & Instruction Address Stack Modules (figs. 2-3, 2-4)

The instruction word stack (IWS) contains twelve 64-bit registers which hold program instruction words for execution. The instruction stack information is essentially a moving window in the program code. Each new word entered in the IWS is entered from memory two words ahead of the program instruction word currently being executed, and at the same time the oldest previously executed instruction word in the stack is discarded. The IWS allows the program to branch back to previously executed instructions still in the IWS without referencing memory.

It may be necessary in program code to occasionally complete a 64-bit instruction word with one parcel pass (0033) instructions. This must be done to avoid starting a two parcel instruction in the fourth parcel of an instruction word. One parcel pass instructions are also used to pad out an instruction word so that the next instruction will be the first parcel of an instruction word (this is necessary for branch entry points because a branch instruction destination address must begin with a new word).

Program instruction words in memory and the IWS are divided into four 16-bit fields called parcels. An 8000 instruction may occupy either 1 or 2 parcels. 1-parcel instructions consist of a 4, 6, or 8 bit instruction codes and two or more designators (i, j, k). In 2-parcel instructions, the k designator is expanded into a 20-bit operand K (see page 1-0 for information on instruction word formats).

| [ | 16 |    | 16 | 1  | 16 | 1  | 15 | 1 |

|---|----|----|----|----|----|----|----|---|

| [ |    | 32 |    | 1  |    | 32 |    | 1 |

| [ | 16 |    |    | 32 |    | 1  | 16 | ] |

| [ | 16 |    | 16 | 1  |    | 32 |    | ] |

| [ |    | 32 |    | i  | 16 | ı  | 16 | ] |

|   |    |    |    |    |    |    |    |   |

Instruction Combinations in Memory and IWS

64-bit instruction words are read up one at a time from the instruction word stack IWS into a 64-bit current instruction word register CIW. From the CIW each instruction word is gated one parcel at a time to the 16-bit instruction parcel translator IPT where each parcel is interpreted for execution. The IPT controls all of the data transmission paths between the sixteen operating registers and the arithmetic units contained in the four register modules and seven functional unit modules (figure 2-2).

```

[ IAS ]

[ Shift Control ]-

IAS

NSA

[ | instruction address stack | ]

from \rightarrow 1 12 ranks of 20-bits | 1-> c

1 1 1

ΙW

[ | |

module [11|10|09 08 07 06 05 04 03 02|01|00] r

P/IAS Coincidence Test

]

-----shift stack--->

* | | | | IWS

P ] v

Register 1 1

1

] |

64-bit words

* 1 1 1

- 1

1

*11|10|09|08 07 06 05 04 03|02|01|00*

**********

1

1 1

0 0

| [ IWS ]-->-|-|-|-|-|-|-|-|-|-|-|

I [ Rank ] v

Branch \ /

address Incre- |

CIW

from ment P I

[ 16 bits > 16 bits > 16 bits > 16 bits ]

RA & RB

modules

0

CIW )

Parcel 1

1 = or

]

[ IPT

[

[

x = and

K ]<-4-[instr.parcel]</pre>

[ translator ]

[ 20 bits ]

[ 16 bits ]

I = IA module

* * = IW module

```

Fig. 2-3 IA and IW MODULES - IWS and CIW Control

Fig. 2-4 IW MODULE - Storage Address Components 2-5

Register Modules (figure 2-5)

#### X registers

16 X registers are the operating registers for each 8000 processor. They are individually designated in this manual by di-bit symbols X00 thru X33. These registers are each 64 bits in length and serve as operand source and destination registers, operand address registers, and indexing registers. Each register is a clear/enter type register with gated clock pulse control. Data will remain in an X register until a control condition generated in the X register access control unit specifically gates a clock pulse to clear the data and enter new data. At most one X register can be cleared and entered with new data at the end of any given clock period.

Communication between the X registers and the arithmetic networks involves a substantial merging of 64-bit data paths and distribution of 64-bit data paths. Almost every arithmetic network has at least one data path to the X registers and one data path from the X registers. The floating point modules have multiple 64-bit paths. The merging and distribution functions are performed in 64-bit static networks preceding and following the X registers.

```

- - floating add

[ XPW register ]

l module

[ mode cond. RA XA FL ]

1 - fl. multiply

l l module

(X) P (Xk)(-Xk) K k - k mask

I I I I I RTC IPF K XA

I I fl. divide

1 1

v v v v

[ 64-bit ]

[ 64-bit ] | [integer] [shift] | [ pack/] | | |

[ operand register A ] | [ adder ] [ ] | [unpack] | | |

1 1 1

boolean

]<-- memory

[

static merge networks

1 modules

X register]

access 1------

control ]

I I I 1 RA module

| | | | | bits 00-15

X registers

| | RB module

| | bits 16-31

64 bits

| | 1 RC module

| 1 bits 32-47

[ | | ]

i, J, k

1 1 1 RD module

[00|01|02|03|10|11|12|13|20|21|22|23|30|31|32|33] bits 48-63

[ Xs,X],Xk ] [

[ selection]--->[ static distribution network [ control ] [

[ control ]

1

1

X }

Χs

Xk

1

1

1

```

Fig. 2-5 REGISTER MODULES RA, RB, RC, RD

#### X RESERVATION FLAGS

There is a reservation flag for each of the sixteen X registers in an 8000 processor. When set, the flags remain set until specifically cleared. Set and clear conditions can never both exist in the same clock period. all X reservation flags are forced clear on dead start.

When the instruction parcel translator (IPT) issues an instruction parcel which designates an X register as the destination register, the reservation flag for that register is set. This flag prevents subsequent instructions from reading the contents of the X register until new data has been transmitted to the register. The contents of an X register is always read one clock period after instruction issue, therefore the reservation flag is cleared 1 clock period before new data is transmitted to the register to allow subsequent instructions to read the new data as soon as it is available.

#### Example:

I<-- CP0 -->I<-- CP1 -->I<-- CP2 -->I<-- CP3 -->I

[ Instr issue, etc.| Read X30, etc. | New data to X30 ]

[ Set X30 flag | Clear X30 flag | ]

Instruction A

[ Instr issue, etc.| Read X30, etc.

[ Set X12 flag | Clear X12 flag

Instruction B

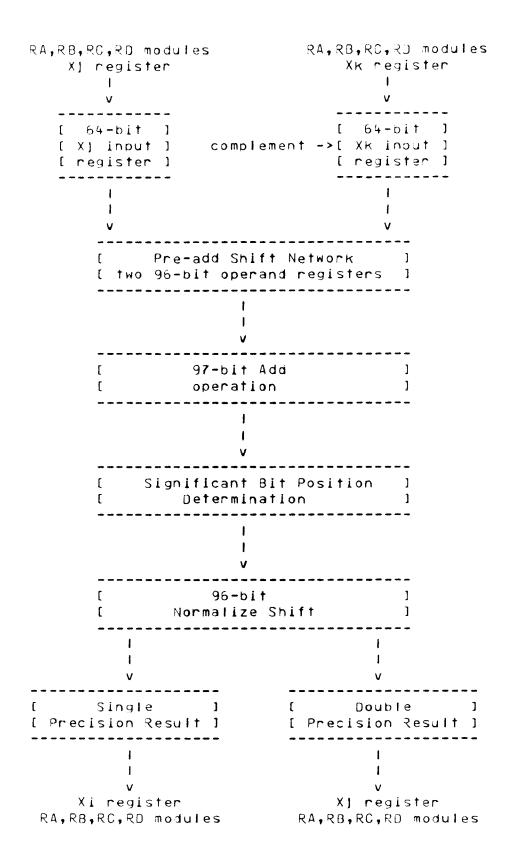

Fig. 2-6 FLOATING ADD MODULES FA, FB

Fig. 2-7 FLOATING MULTIPLY MODULES MA, MB, MC

#### 8600 MEMORY

The overall organization of the 8600 memory is shown in figure 2-10 on the following page. Storage addresses arrive at the storage address stack (SAS) from the IW module. The storage access control (SAC) unit determines the oriority of storage access requests when two requests occur simultaneously. SAC also controls the entry of addresses into the storage address stack (SAS). When the SAS data backs up because of memory conflicts, the SAC stops instruction issue until the conflicts have been resolved.

The storage word stack (SWS) is a buffer area for 64-bit data words which are to be written into memory.

The 64 memory bank modules provide a linear selection type core memory with a total capacity of 256K words of 64-bit length (K = 1024). Each 64-bit word is addressed separately. The memory is arranged in 64 banks (one bank per memory bank module) of 4K words each. Each bank is independent of the other 63 banks.

The maximum data transfer rate between memory as a unit (64 banks) and other parts of the system is one word each clock period. Each memory bank has a nine?? clock period access time from arrival of the storage address to readout of the 64-bit word. The total read/write cycle time for a memory bank is 32?? clock periods. In random addressing of memory by all four processors for program data, instructions, and input/output channel data, an average rate of 10 to 15??? memory banks in operation at one time is anticipated.

```

PO <----1

RA, RB, RC, RD

P1 <---64-----

I/0

P2 <---1

Λ

modules

P3 <----1

1

1

PO <---64----1

68

ΙW

P1 <----1

-1

P2 <----1

modules

P3 <---1

I/0

1 read 1

data 1

IQ module

1

1

-[ MEMORY

5 0

] ]

BANK

MODULES 1

]]-

P0 IW ---20--> -----

0000MM ]]]

STORAGE

-[[-----

[

[[[ MM0001 ]

P1 IW ---20--> [

ACCESS

address

]----->

-[[-----

CONTROL

P2 IW ---20--> [

[[[ MM0001 ]

STORAGE 1

[ SA

ADDRESS 1

-[[-----

[[[ MM0003 ]

P3 IW ---20--> -----

-[[-----

[[[ MM0010 ]

-[[-----

[[[ MM0011 ]

go write

-[[-----

[[[ MM0012 ]]

PO X reg --64-> -----

STORAGE 1

....

[

-[[------

[[[ MM0321 ]

P1 X reg --64-> [

WORD STACK 1 write data

& PARITY 1---- 68 ---->

P2 X reg --64-> [

GENERATE 1

-[[-----

[[[ MM0322 ]

[ SW MODULE ]

-[[-----

[[[ MM0323 ]

P3 X reg --64-> -----

1

[[ MM0330 ]

64

-[[-----

[[[ MM0331 ]

1

- [

[[-----

1/0

IQ module

[ MM0333 ]

```

Fig. 2-10 8600 MEMORY

```

SA module

go write via MM module

SW module

via MM module

- 1

1

1

12

68

-1

[ 12-bit

[ go ]

write register | spares |

[write] [ address register ]

[ FF ]

-

72

1

[ 16 x 256

[ read/write drive ckt. ]

[ combinations ]

go -->[ & ]

write ----

module stack

---- [ 72 ] [ module stack [ 1 ]-72->[ augment ]->---- [ generators ] | [ sixteen 72 x 256 planes

go -->[ & ]

sense

write ----

amplifiers ]

inverted A

- 72- -

72-bit

read register

1

F

1

5.8

64

1

.

V

V

IW module I/O X reg. X reg. modules

```

Fig. 2-12 MEMORY BANK MODULE MM

```

64-bit

SWS RANKS

64

bits [ ]--->[ A ]--->[ ]

from ---->[select] ----- [ select ]

[ rank ]--->[ 8 ]--->[ and ]

[ PO ] ----- [ merge ]\

Go enter ->[ ]--->[ C ]--->[ ] \

Go exit

64

[ ]--->[ A ]--->[

bits

from ---->[select] ------[

[ rank ]--->[ B ]--->[ select ]

[ P1 ] ----- [ and ]

Go enter ->[ ]--->[ C ]--->[ merge ]

-->[

/

---- [

[ Parity ]--> MM

----/ ^ I

-->[ 4-bits ] modules

54 bits

from I/O --->[ ]---->[ I/O ] Go exit v v

[ & ] -----

[ 54-bit ]/

Go enter --->[ ]

[ merge ]

[register]\

[ 64-bit ]

-->[ exit ]--> MM

64

[register] modules

bits [ ]--->[ ]

from ---->[select] ----- [ select ] |

[ rank ]--->[ B ]--->[ and ]

[ P2 ] ----- [ merge ]

Go enter ->[ ]--->[ ]

Go exit

64

[ ]--->[ A ]---->[ ] /

from ---->[select] ----- [ select ]/

[ rank ]--->[ B ]--->[ and ]

[ P3 ] ----- [ merge ]

Go enter ->[ ]--->[ C ]--->[ ]

Go exit

I/O ----->[ ]

PO ----->[ Go ]

P1 ---->[ write ]----> MM

P2 ---->[ merge ] modules

P3 ---->[ ]

```

Fig. 2-13 STORAGE WORD STACK MODULE SW

```

[ DATA & 1-- 54-bit -> SW

>[ FAN-IN

l write module

]

MODULE 1-- 20-bit -> SA

[[]

l address module

64 bits write data

& 20 bits address

[ DATA FAN-OUT]

[ PARITY CHK ] <- 68-bit -- MM

1/

[ RTC MODULE ]

read module

---[ CHANNEL

}

54

]<---- bits ----[</pre>

[ [

MODULES

1-- 4x20 --> IW

read data [IR

[ [ [IP Ch 00-03 ]<---

modules

P0-P3

[ [IP Ch 10-13 ]

2.0

bits

begin.

[IP Ch 30-33 ]

address

]

Xk beginning

[ I/O CONTROL ]

address

- 1

---[ MODULE ]<-- 4x20 --- DB

modules

1

]

12 12

P0-P3

[ [ 0

1

1

External

DB modules

I/0

Station

/

4x20

[ PAR.ADD.REG.]<--

[INTERLOCK REG]

[ MASTER CLOCK] <-- 4x20 --- IW

[ MODULE ]

modules

[ IS

] < - -

4×20

memory addr.

SA modules

```

Fig. 2-14 8500 I/O SECTION

#### EXCHANGE PACKAGES

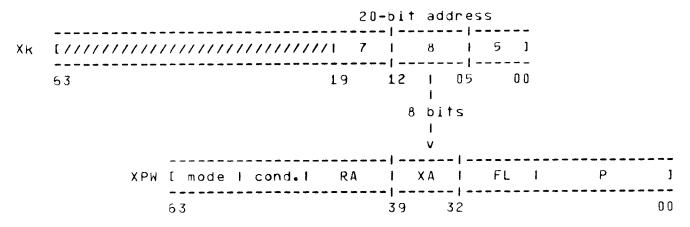

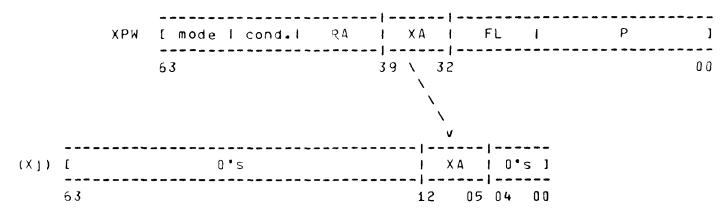

An exchange package consists of sixteen 64-bit data words (XDW) and one 64-bit exchange parameter word XPW. The RA and FL fields in the exchange parameter word specify storage increments of 256 word units. XA specifies exchange package location with the lowest order 5 bits removed.

| mode condition |  |  | RA | <br>ХД | FL   | <br>Р |   |

|----------------|--|--|----|--------|------|-------|---|

|                |  |  |    |        |      | 2 0   | ] |

|                |  |  |    | <br>   | <br> | <br>  |   |

Exchange Parameter Word

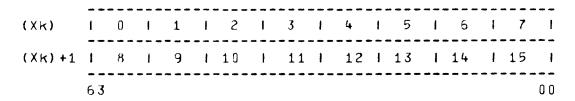

The exchange package resides in low storage addresses at address multiples of 32. The X register data words XDW appear first in memory followed by the exchange parameter word XPW. The 15 locations following an exchange package can be used for system functions related to the exchange package.

|    | memory                                |            |

|----|---------------------------------------|------------|

| 0  | [<br>[<br>[<br>[<br>[                 | ]          |

| 32 | [ XDW [ (16 words) [ [ XPW (1 word) ] | ]          |

| 64 | [ XDW [ (16 words) [ [ XPW (1 word) ] | ]          |

| 96 | [                                     | ]<br><br>] |

|    | [ [ XPW                               |            |

An exchange sequence moves the exchange parameter word first, followed by the OO register data and the other registers in order. The exchange parameter word (XPW) for the arriving exchange package goes into the XO register for one clock period, and later moves into a holding register in the register modules (XPW register).

| n(32) | t x 0 0                                    |            | )                   |

|-------|--------------------------------------------|------------|---------------------|

| + 1   | [ X01                                      |            | ]                   |

| + 2   | [ X02                                      |            | ]                   |

| + 3   | [ X 0 3                                    |            | ]                   |

| + 4   | [ X10                                      |            | ]                   |

| + 5   | [ X11                                      |            | ]                   |

| + 6   | [ X12                                      |            |                     |

| + 7   | [ X13                                      |            | ]                   |

| + 8   | [ X20                                      |            | 1                   |

| + 9   | [ X21                                      |            | 1                   |

| +10   | [ X22                                      |            | 1                   |

| +11   | [ X23                                      |            | 1                   |

|       |                                            |            | 1                   |

| +12   | [ X30                                      |            | j                   |

| +13   | [ X31                                      |            | ]                   |

| +14   | [ X32                                      |            | ]                   |

| +15   | [ X33                                      |            | ]                   |

| +16   | [ mode   cond.  RA   XA                    | FL         | P ]                 |

|       | 63 60 59 52 51 40 39 32 31                 |            | 20 19 0             |

|       |                                            |            |                     |

| bi    | MODE FLAGS                                 | bit        | CONDITION FLAGS     |

| 63    |                                            | 59         | Object program call |

|       | prevents interrupt                         | 58         | I/O channel request |

| 62    | PRF - program reference flag<br>adds RA to | 5 <b>7</b> | Time interval       |

|       | program address                            | 56         | System call         |

| 61    | •                                          | 55         | Data field limit    |

|       | allows access to                           | <b>-</b> , |                     |

overflow/indefinite 52

interlock register

interrupts on FP

60 OVF - FP interrupt

54 Program field limit

Program error exit

Overflow / indefinite

53

#### I/O CHANNEL REQUEST

A channel request mechanism is common to all I/O channels. This mechanism is activated by an input RF. The channel number is encoded and presented to all processors over a 4-bit channel request path.

The channel request mechanism scans the processors for a processor with no monitor flag. When one is found, the channel request flag is set in the processor XPW register.

This causes an exchange exit to a monitor program which can read the object program parameter word and determine the cause of the exit. The monitor program can then read the 4-bit channel number from the channel request path. The reading process advances the channel request mechanism to the next channel request, if any.

The monitor program uses the 4-bit channel number for a table lookup to determine the mode of the requesting channel. If the request can be satisfied by the monitor program, the interrupted object program is resumed. If a new program must be initiated, the monitor program updates the running time for the terminated program and exchanges to a new XA.

#### FLOATING POINT ARITHMETIC

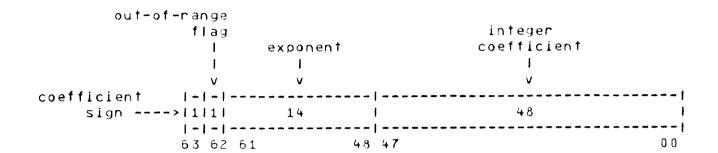

Floating point arithmetic calculations are performed in the 8000 processors using a packed 64-bit format for number representation. This format represents a signed binary integer coefficient times two with a signed binary integer exponent. The coefficient field contains 49 bits and the exponent field 14 bits. The remaining bit is used to indicate an out-of-range condition.

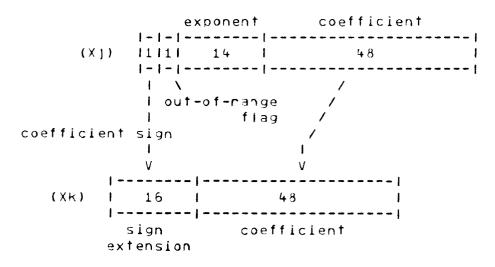

Floating point format

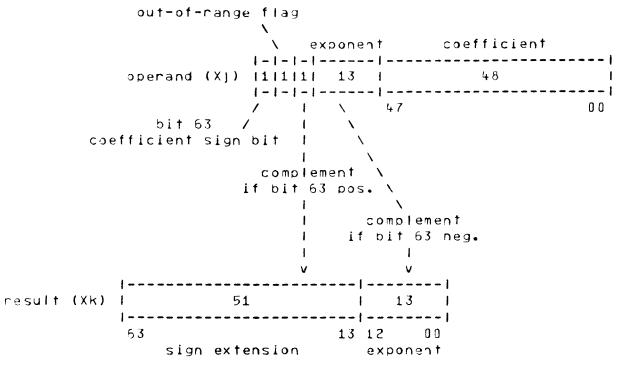

The coefficient field in the floating point format is not contiguous. The sign of the coefficient occupies the highest order bit position in the 64-bit word. The remainder of the coefficient resides in the lowest order 48 bit positions. If the exponent field and the error flag are replaced with copies of the sign bit (as in the unpack instruction 0110) the resulting format is the normal integer representation.

The exponent field in the floating point format occupies the bit positions 2\*\*48 through 2\*\*61. This field represents exponent values ranging from 2\*\*(-13) to 2\*\*(+13). The bits in the exponent field in the packed floating point format consist of the bits in the integer exponent (in ones complement form) with the highest order bit complemented. The complementing of the highest order exponent bit results in a format which represents the floating point numbers in such a way that their increasing values are also monotonically increasing when viewed as 64\*bit integers. As a result of this property, comparison tests of two floating point quantities can be done in the integer adder rather than in the slower floating point adder. Floating point quantities with negative coefficients are packed with the exponent field complemented in order to preserve the above relationship for negative numbers.

Bit position 2\*\*62 in the floating point format contains the out-of-range flag. This flag is set when the exponent in a floating point calculation exceeds 2\*\*(+13) or if the result is indefinite. This flag is considered set when the values of the two highest order bits in the floating point format disagree. Further floating point operations in which this flag appears set in one of the operands results in aborting the normal sequence and generating a result with the out-of-range flag set.

Floating point calculations which underflow the exponent range are aborted and the result replaced with a word of all zero bits.

#### BINARY ARITHMETIC

Binary arithmetic in the 8000 processors is performed in a modified ones complement additive mode. The sum of two binary numbers in a normal ones complement additive mode is defined by the recursive Boolean expressions below.

```

Let m = number of bit positions in adder

A(i) = addend bit i

B(i) = augend bit i

C(i) = carry into bit position i

S(i) = sum bit i

Where i = 0,1,2,3,4,...,m-1

Then C(i+1) = A(i).and.B(i).or.B(i).and.C(i).or.C(i).and.A(i)

C(0) = C(m)

S(i) = A(i).and..not.B(i).and..not.C(i).or.

B(i).and..not.C(i).and..not.A(i).or.

C(i).and..not.A(i).and..not.B(i).or.

A(i).and.B(i).and.C(i)

```

The modification to the above mode consists of replacing a resulting sum of all one bits with a result of all zero bits. An 8000 processor adder therefore has only one form of zero as a resulting sum.

Subtraction is performed by complementing the subtrahend and adding to the minuend.

# Part 3 INSTRUCTION DESCRIPTIONS

# 8000 INSTRUCTION CODES

| Read program (P + K) to X] Transmit P + K to X] Transmit K to X] Transmit K to X]             | Set IP flags from Xk (IPF)<br>Clear IP flags from Xk (IPF)<br>Read IP flags to Xj<br>Read internal clock to Xj | Jump to P + K Call subroutine at P + K Jump to P + K if X] in range Jump to P + K if X] error  | Jump to P + K if X] is zero  Jump to P + K if X} not zero  Jump to P + K if X] positive  Jump to P + K if X] negative | Call subroutine at K Call subroutine at XK Call libr. routine at K [cl PRF] Call libr. routine at XK | Subroutine exit to X] + k<br>Lib. exit to X] + k [set/cl PRF]<br>Jump to K<br>Exchange exit                | Save lower XJ for n bits<br>Blank lower XJ for n bits<br>Left shift XJ by n bits<br>Right shift XJ by n bits | Integer X] + K to Xi<br>Integer X] + Xk to Xi<br>Integer X] - Xk to Xi | Floating X] + XK to Xi<br>Floating X] - XK to Xi<br>Floating X] * XK to Xi<br>Jump to P - i if X] < XK         | Read data (X) + K) to Xi Read data (X) + Xk) to Xi Store data (X) + K) from Xi Store data (X) + Xk) from Xi |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 0220<br>0221<br>0222<br>0223                                                                  | 0231<br>0231<br>0232<br>0233                                                                                   | 0301<br>0301<br>0302<br>0303                                                                   | 0311<br>0311<br>0312<br>0313                                                                                          | 0320<br>0321<br>0322<br>0323                                                                         | 0331<br>0331<br>0332<br>0333                                                                               | 100X<br>101X<br>102X<br>103X                                                                                 | 111XX<br>12XX<br>13XX                                                  | 20 X X 2 2 2 X X X 2 2 2 X X X 2 2 3 X X X 2 3 X X X 2 3 X X X X                                               | 30 X X X X X X X X X X X X X X X X X X X                                                                    |

| Program error exit<br>Logical X] * Xk to XJ<br>Logical X] + Xk to XJ<br>Logical X] - Xk to XJ | Copy Xk to Xj<br>Complement Xk to Xj<br>Shiff Xj left by Xk<br>Shiff Xj right by Xk                            | Floating DP X) + Xk to X) Floating DP X) - Xk to X) Floating X) / Xk to X) Population Xk to X) | Floating DP X] * XK to X]<br>Integer X] * Xk to Xj<br>Program error exit<br>Pass                                      | Transmit k to X) Transmit -k to X) Integer X) + k to X) Integer X] - k to X)                         | Unpack coefficient XJ to Xk<br>Unpack exponent XJ to Xk<br>Pack Xk * 2 ** XJ to Xk<br>Integer 0 - Xk to XJ | Begin system call [MTF]<br>End system call [MTF]<br>Channel XJ to (Xk) [MTF]<br>Channel XJ from (Xk) [MTF]   | Channel request to XJ [MTF] Load XA from XK [MTF] Program error exit   | Store data (K) from XJ<br>Store data (Xk) from XJ<br>Read/store data (K) and XJ<br>Read/store data (Xk) and XJ | Read data (K) to Xj<br>Read data (Xk) to Xj<br>Read program (K) to Xj<br>Read program (Xk) to Xj<br>3-0     |

| 00 00<br>00 01<br>00 02<br>00 03                                                              | 0010<br>0011<br>0012<br>0013                                                                                   | 0020<br>0021<br>0022<br>0022                                                                   | 0930<br>0031<br>0032<br>0033                                                                                          | 0100<br>0101<br>0102<br>0103                                                                         | 0110<br>0111<br>0111<br>0112                                                                               | 0120<br>0121<br>0122<br>0123                                                                                 | 0130<br>0131<br>0132<br>0133                                           | 0200<br>0201<br>0201<br>0202<br>0203                                                                           | 0210<br>0211<br>0212<br>0213                                                                                |

## NOTES

1. The following pages of instruction descriptions are numbered with the instruction codes shown in the box in the upper right corner of each page. The instruction codes are shown in quaternary or dibit notation and parenthetically in hexidecimal notation.

| [ 0331 ]    | [ 103X ]    | [ 23XX ]    |

|-------------|-------------|-------------|

| [ ]         | [ ]         | [ ]         |

| [ (3D) ]    | [ (40) ]    | ( (Bx) ·]   |

|             |             |             |

| 8-bit       | 6-bit       | 4-bit       |

| Instruction | Instruction | Instruction |

| code        | code        | code        |

2. This section makes extensive use of abbreviations and special terms which are listed in the index in Appendix A together with a reference to the page where each term is defined.

Parenthesis are used to indicate the contents of a register, e.g., (X) indicates the contents of the X register specified by the J designator.

[ 0000 ]

[ ]

[ 0000xxxx | Program error exit [ (00) ]

This instruction format is treated as an error condition and, if executed, will set the program error exit flag in the exchange parameter word (XPW). This condition flag will then cause an exchange jump to address (XA). In this case all instructions which have issued prior to this instruction will be run to completion. Any instructions following this instruction in the current instruction word will not be executed. When all operands have arrived at the operating registers as a result of the previously issued instructions, an exchange jump will occur to the exchange package which is designated by (XA).

The ] and k designators in this instruction are ignored. The program address stored in the exchange package on the terminating exchange jump is advanced one count from the address of the current instruction word. This is true no matter which parcel of the current instruction word contains the program error exit instruction.

This instruction format is not intended for use in normal program code. The program error exit flag is set in the exchange parameter word (XPW) to indicate that the program may be in range but is not executing valid program code. This could occur when an incorrectly coded program jumps into an unused area of the memory field or into a data field.

|   |           |   |         |         |     |      |     |      |     |     |     |   | - |

|---|-----------|---|---------|---------|-----|------|-----|------|-----|-----|-----|---|---|

|   | <b></b> - |   |         |         |     |      |     |      |     |     | 000 | 1 | 3 |

| 1 | 0001]]kk  | 1 | Logical | product | o f | (X)) | and | (XK) | t o | X } | [   |   | ] |

|   |           |   | -       |         |     |      |     |      |     |     | (01 | ) | } |

|   |           |   |         |         |     |      |     |      |     |     |     |   | _ |

This instruction causes operands to be read from the XJ and Xk registers, forms a bit-bit logical product, and enters the result in the XJ register. Each of the bits in (XJ) is acted upon by the corresponding bit of (Xk) to form a single bit in the result entered in the XJ register. A sample computation is listed below in di-bit notation to illustrate the operation performed and includes the four possible bit combinations that may occur.

This instruction is intended for extracting portions of a 64-bit word during data processing as distinguished from numerical computation. Together with other boolean and shift instructions it may be used to manipulate alphanumeric or other coded data not related to the 64-bit machine word length.

## ISSUE CONDITIONS

X) register is free one clock period after instruction issues Xk register is free one clock period after instruction issues X register input path is free two clock periods after issue

### EXECUTION TIMING

No execution delays possible after this instruction issues from IPT.

- CPO Instruction issues from IPT

Transmit ] and k designators to register modules

Set X] reservation flag

- CP1 Read (X)) to operand register A

Read (Xk) to operand register 8

Clear X) reservation flag

- CP2 Transmit logical product of (A) and (B) to X]

#### NOTES

1. If the f and k designators have the same value this instruction will read a 64-bit word from the designated X register and then write the same information back into that X register. The timing for this case will be the same as the timing for the general case, and no special conflicts will occur.

|                                                | [ 0002 ] |

|------------------------------------------------|----------|

| 0002  kk   Logical sum of (X)) plus (Xk) to X) | [ ]      |

|                                                | [ (02) ] |

|                                                |          |

This instruction causes operands to be read from the XJ and Xk registers, forms a bit-bit togical sum, and enters the result in the XJ register. Each of the 64 bits in (XJ) is acted upon by the corresponding bit of (Xk) to form a single bit in the result entered in the XJ register. A sample computation is listed below in di-bit notation to illustrate the operation performed and includes the four possible bit combinations that may occur.

This instruction is intended for merging portions of a 64-bit word into a composite word during data processing as distinguished from numerical computation. Together with the other boolean and shift instructions it may be used to manipulate alphanumeric or other coded data not related to the 64-bit machine word length.

# ISSUE CONDITIONS

X) register is free one clock period after instruction issues Xk register is free one clock period after instruction issues X register input is free two clock periods after issue

## EXECUTION TIMING

No execution delays possible after this instruction issues from IPT.

- CPO Instruction issues from IPT

Transmit | and k designators to register modules

Set X| reservation flag

- CP1 Read (X]) to operand register A Read (Xk) to operand register B Clear X] reservation flag

- CP2 Transmit logical sum of (A) and (B) to XJ

#### NOTES

1. If the J and k designators have the same value this instruction will read a 64-bit word from the designated X register and then write the same information back into that X register. The timing for this case will be the same as the timing for the general case, and no special conflicts will occur.

|                                                        | [ 0003 ] |

|--------------------------------------------------------|----------|

| 0003]]kk   Logical difference of (X]) minus (Xk) to X] | [ ]      |

|                                                        | [ (03) ] |

|                                                        |          |

This instruction reads operands from the XJ and Xk registers, forms the bitaby-bit logical difference of (XJ) minus (XK), and enters the resulting 64-bit word in the XJ register.

| Sample operands: | (X)) = 1010 |

|------------------|-------------|

| (lower 4 bits)   | (Xk) = 1100 |

| (binary)         |             |

|                  | (XI) = 0110 |

This instruction is intended for comparing bit patterns or for complementing bit patterns during data processing as distinguished from numerical computation. Together with the other boolean and shift instructions it may be used to manipulate alphanumeric or other coded data not related to the 64-bit machine word length.

# ISSUE CONDITIONS

X) register is free one clock period after instruction issues Xk register is free one clock period after instruction issues X register input path is free two clock periods after issue

# EXECUTION TIMING

No execution delays possible after this instruction issues from IPT.

- CPO Instruction issues from IPT

Transmit ] and k designators to register modules

Set X] reservation flag

- CP1 Read (X)) to operand register A Read (Xk) to operand register B Clear X) reservation flag

- CP2 Transmit logical difference of (A) and (B) to XI

# NOTES

1. If the 1 and k designators have the same value in this instruction, a logical difference is formed between two identical quantities. The result will be a word of all 0's written into register X1. The timing for this case is the same as the timing for the general case.

| 1 | 0010]]kk | Copy | (XK) | to | X |

|---|----------|------|------|----|---|

|   |          |      |      |    |   |

This instruction reads a 64-bit word from the Xk register and enters the word in the XJ register.

This instruction is intended for moving data from one X register to another X register as rapidly as possible. No logical function is performed on the  ${\tt data}$ .

## ISSUE CONDITIONS

X) register is free one clock period after instruction issues Xk register is free one clock period after instruction issues X register input path is free two clock periods after issue

#### EXECUTION TIMING

No execution delays possible after this instruction issues from IPT.

- CPO Instruction issues from IPT

Transmit ] and k designators to register modules

Set X] reservation flag

- CP1 Read (Xk) to operand register B

Clear XJ reservation flag

- CP2 Transmit (B) to X1

## NOTES

1. If the ) and k designators have the same value this instruction will read a 64-bit word from the designated X register and then write the same information back into that X register. The timing for this case will be the same as the timing for the general case, and no special conflicts will occur.

| _ |          |   |      |            |     |      |     |    |

|---|----------|---|------|------------|-----|------|-----|----|

| J | 0011jjkk | 1 | Copy | complement | o f | (XK) | t o | Χј |

| - |          |   |      |            |     |      |     |    |

[ 0011 ]

This instruction reads a 64-bit word from the Xk register, complements the tne word, and enters the result in the XJ register.

This instruction is also useful in data processing for inverting an entire 64-bit field. The 1 and k designators may frequently have the same value because the result may often be returned to the same X register.

#### ISSUE CONDITIONS

X) register is free one clock period after instruction issues Xk register is free one clock period after instruction issues X register input path is free two clock periods after issue

### EXECUTION TIMING

No execution delays possible after this instruction issues from IPT.

- CPO Instruction issues from IPT

Transmit J and k designators to register modules

Set XJ reservation flag

- CP1 Read (Xk) complement to operand register B

Clear X) reservation flag

- CP2 Transmit (B) to Xj

# NOTES

1. The J and k designators may frequently have the same value in this instruction. In this case, the quantity read from the designated X register is complemented and returned to the same X register. The Timing is the same as for the general case.

This instruction reads a 64-bit operand from the X] register, shifts the operand left or right as specified by (Xk), and enters the resulting operand back into the X] register. If (Xk) is positive, the data is shifted left circularly the number of bit positions designated by (Xk). If (Xk) is negative the data is shifted right (end off) with sign extension the number of bit positions designated by the magnitude of (Xk). Sample shift operations are listed below in binary notation.

Sample (64 bits): (X) operand = 10110000....00000000 (Xk) = 0..0100 (X) result = 00000000....00001011

Sample (64 bits): (X) operand = 01100000....00001000 (Xk) = 1..1101 (X) result = 00011000....00100010

Sample (64 bits): (X) operand = 11000000....00100010 (Xk) = 1..1100 (X) result = 11111000....00100110

This instruction is for use in data processing where the shift count (Xk) is derived by program computation. It is also used for generating a truncated integer from the coefficient of a floating point number when the exponent has been unpacked into an X register.

### ISSUE CONDITIONS

XI register is free one clock period after instruction issues Xk register is free one clock period after instruction issues X register input path is free three clock periods after issue

#### EXECUTION TIMING

No execution delays possible after this instruction issues from IPT.

- CPO Instruction issues from IPT Set XI reservation flag

- CP1 Read (X)) to operand register A Read (Xk) to operand register B

- CP2 Begin operand shift

Clear XI reservation flag

- CP3 Complete operand shift Transmit result to XJ

#### NOTES

- 1. The maximum shift count which may be specified by (Xk) is 63 decimal.

- 2. If (Xk) is 0 (either all 1's or all 0's binary) the instruction reads the operand from register X) and returns it unaltered to register X). The timing for this case is the same as for the general case.

This instruction reads a 64-bit operand from the XJ register, shifts the operand right or left as specified by (Xk), and writes the resulting operand back into the XJ register. If (Xk) is positive, the operand is shifted right (end off) with sign extension the number of bit positions designated by (Xk). If (Xk) is negative, the operand is shifted left circularly the number of bits designated by the magnitude of (Xk). Sample shift operations are listed below in binary notation.

```

Sample (64 bits): (X) operand = 10110000.....00000000

(XK) = 0..0100 (X) result = 11111011.....000000000

Sample (64 bits): (X) operand = 01100000.....00001000

(XK) = 1..1101 (X) result = 100000000.....00100001

```

This instruction is for use in data processing where the shift count (Xk) is derived by program computation.

## ISSUE CONDITIONS

XJ register is free one clock period after instruction issues XK register is free one clock period after instruction issues X register input path is free three clock periods after issue

### EXECUTION TIMING

No execution delays possible after instruction issues from IPT.

- CPO Instruction issues from IPT Set XI reservation flag

- CP1 Read (X)) to operand register A

Read (Xk) complement to operand register B

- CP2 Begin operand shift

Clear XJ reservation flag

- CP3 Complete operand shift Transmit result to XI

#### NOTES

1. The maximum shift count which may be specified by (Xx) is 63 decimal.

| 1 0020]]kk 1 | Floating double precision sum |

|--------------|-------------------------------|

|              | of (XJ) olus (Xk) to XJ       |

[ 0020 ] [ ] [ (08) ]

This instruction forms the floating double precision sum of two floating point operands read from the XI and Xk registers, and enters the lower half of the result in the XI register.

The two operands are not rounded in this operation and may or may not be normalized. They are unpacked from floating point format and the exponents compared. The coefficient with the smaller exponent is shifted down by the difference of the exponents so as to align bits of corresponding significance, and a 97-bit adder forms a double precision 1's complement sum. The exponent of the 48-bit lower half coefficient entered in X1 is 48 decimal less than the exponent of the upper half coefficient.

The 97-bit result is normalized following the add operation. The result coefficient is displaced right one bit or left up to 64 bits and the result exponent is incremented or decremented by the shift count.

Since the double precision sum is normalized, the upper half result is normalized, but the lower half result is not.

A zero result from this instruction is always a positive zero.

This instruction is intended for use in floating point calculations involving double precision or multiple precision. Used together with the single precision FP sum instruction 20XX, this instruction forms a double precision sum in two X registers with no loss of precision.

## ISSUE CONDITIONS

X) register is free one clock period after instruction issue Xk register is free one clock period after instruction issue X register input path is free eight clock periods after issue

## EXECUTION TIMING

No\_execution delays possible after this instruction issues from IPT.

# EXECUTION TIMING (continued)

CPO Instruction issues from IPT Transmit 1 and k designators to register modules Set X<sub>j</sub> reservation flag CP1 Read (X)) to floating add module FA Read (Xk) to floating add module FA Compare exponents Transmit coefficients to pre-add shift register CP2 Select smaller exponent CP3 Shift coefficients for bit alignment Transmit coefficients to 97-bit adder CP4 Form double precision sum CP5 Transmit DP sum to bit position network CP6 Determine significant bit position Transmit result to shift network CP7 Perform 96-bit normalize shift Clear X] reservation flag

Enter lower half of result in XI

CP8

|                                                   | [ 0021 ] |

|---------------------------------------------------|----------|

| 1 0021]]kk   Floating double precision difference | [ ]      |

| of (X) minus (Xk) to X)                           | [ (09) ] |

|                                                   |          |

This instruction forms the floating double precision difference of two floating point operands read from the  $X_1$  and  $X_2$  registers, and enters the lower half of the  $(X_1)$  minus  $(X_2)$  result in the  $(X_1)$  register.

The two operands are not rounded in this operation and may or may not be normalized. (X) and complemented (Xk) are unpacked from floating point format, the coefficient with the smaller exponent is shifted down by the difference of the exponents, and a 97-bit adder forms a double precision 1's complement sum. The exponent of the 48-bit lower half coefficient entered in XJ is 48 decimal less than the exponent of the upper half coefficient.

The 97-bit result is normalized following the add operation. The result coefficient is desplaced right one bit or left up to 54 bits and the result exponent is incremented or decremented by the shift count.

Since the double precision difference is normalized, the upper half result is normalized, but the lower half result is not.

This instruction is intended for use in floating point calculations involving double precision or multiple precision. Used together with the single precision FP difference instruction 21XX, this instruction forms a 96-bit double precision difference in two X registers with no loss of precision.

## ISSUE CONDITIONS

X) register is free one clock period after instruction issues Xk register is free one clock period after instruction issues X register input path is free eight clock periods after issue

## EXECUTION TIMING

No execution delays possible after this instruction issues from IPT.

## EXECUTION TIMING (continued)

- CPO Instruction issues from IPT

Transmit ) and k designators to register modules

Set X) reservation flag

- CP1 Read (X]) to floating add module FA

Read complement of (Xk) to floating add module FA

Compare exponents

Transmit coefficients to pre-add shift register

- CP2 Select smaller exponent

- CP3 Shift coefficients for bit alignment Transmit coefficients to 97-bit adder

- CP4 Form doubte precision sum

- CP5 Transmit DP sum to bit position network

- CP6 Determine significant bit position Transmit result to shift network

- CP7 Perform 96-bit normalize shift Clear XJ reservation flag

- CP8 Enter lower half of result in XI

|                                                  |           | - |

|--------------------------------------------------|-----------|---|

|                                                  | 0022      | ] |

| 0022]]kk   Floating divide of (XJ) by (Xk) to XJ | [         | ] |

|                                                  | ( ( O A ) | ] |

|                                                  |           | _ |

This instruction reads operands from the X) and Xk registers, forms a floating point quotient, and delivers this result to the X) register. The dividend operand is (X) and the divisor operand is (Xk). The remainder from the division process is discarded.

The operands are assumed to be numbers in floating point format. If the divisor operand is not normalized, the out-of-range flag is set.

## ISSUE CONDITIONS

XI register is free one clock period after instruction issues Xk register is free one clock period after instruction issues X register input path is free clock periods after issue

EXECUTION TIMING

|                                             | [ 0023 ] |

|---------------------------------------------|----------|

| 1 0023]]kk   Population count of (Xk) to Xj | [ ]      |

|                                             | [ (80) ] |

|                                             |          |

This instruction reads an operand from the Xk register, counts the number of 1 bits in the operand, and enters the count in the XJ register. The word entered in XJ is in positive integer format. If (Xk) is all 1\*s, a count of 64 decimal is entered in the XJ register. If (Xk) is all 0\*s, a zero word is entered in the XJ register.

This instruction is intended for use in data processing where a degree of coincidence is desired.

#### ISSUE CONDITIONS

X) register is free one clock period after instruction issues Xk register is free one clock period after instruction issues X register input path is free five clock periods after issue

### EXECUTION TIMING

No execution delays possible after this instruction issues from IPT

- CPO Instruction issues from IPT

Transmit | and k designators to register modules

Set X| reservation flag

- CP1 Read (Xk) to input register in DA module

- CP2 Form partial sums

- CP3 Form partial sums

- CP4 Form count result in D3 module Clear X1 reservation flag

- CP5 Transmit result to XI in register modules

## NOTES

1. If the J and k designators have the same value, the operand is read from and the count stored back into the same X register.

|                                              | [ 0030 ] |

|----------------------------------------------|----------|

| 0030]]kk   Floating double precision product | [ ]      |

| of (X) times (Xk) to X)                      | [ (00) ] |

|                                              |          |

This instruction reads two normalized floating point operands from the X) and Xk registers, forms a floating point double precision product, and enters the lower half of the result in the X) register.

The two operands are unpacked from floating point format (the operands are not rounded). The exponents are added to determine the exponent for the result. The result exponent is 48 decimal less than the exponent of the upper half coefficient (the upper half coefficient is extracted with the 13XX instruction).

The coefficients are multiplied as signed integers to form a 96-bit double precision integer product. The lower half of this product is then extracted to form the 48-bit coefficient for the result. If the double precision product has only 95 significant bits, a 1-bit normalizing shift is performed before extracting the lower half, and the exponent for the result is decremented by one count.

This instruction is intended for use in multiple precision floating point calculations. Used together with the single precision FP multiply instruction 22XX, this instruction forms a 96-bit double precision product in two X registers with no loss of precision.

# ISSUE CONDITIONS

X) register is free one clock period after instruction issues Xk register is free one clock period after instruction issues X register input path is free eight clock periods after issue

## EXECUTION TIMING

No execution delays possible after this instruction issues from IPT.

[ 0030 ] [ ] [ (0C) ]

# EXECUTION TIMING (continued)

CPO Instruction issues from IPT Transmit ) and k designators to register modules Set X) reservation flag CP1 Transmit (X) and (Xk) to floating multiply module MA Separate exponents from coefficients CP2 Perform sign corrections Form first 16x48 product CP3 Form second 16x48 product Form third 16x48 product CP4 CP5 Merge the three 16x48 products into 96-bit result register CP7 Clear XI reservation flag CP8 Enter lower 48 bits of 96 bit result and exponent result in XJ

(entire 64-bit result complemented if negative)

| 0031]]kk | Integer product of (X)) times (Xk) to X)

[ 0031 ] [ ] [ (0D) ]

This instruction reads two operands (limited to 48 bits plus sign and sign extension) from the XJ and Xk registers, forms the product, and delivers the result to the XJ register.

The instruction is performed in the floating multiply unit (the exponent arithmetic portion is not used).

The operands are multiplied as signed integers to form a 96-bit product. The lower 64 bits of this product are extracted and entered in the XJ register.

### ISSUE CONDITIONS

X) register is free one clock period after instruction issues Xk register is free one clock period after instruction issues X register input path is free eight clock periods after issue

#### EXECUTION TIMING

No execution delays possible after this instruction issues from IPT.

- CPO Instruction issues from IPT

Transmit | and k designators to register modules

Set X| reservation flag

- CP1 Transmit (X)) and (Xk) to floating multiply unit Perform sign corrections

- CP2 Form first 16x48 product

- CP3 Form second 16x48 product

- CP4 Form third 16x48 product

- CP5 Merge the three 16x48 products into 96-bit result register

- CP7 Clear XJ reservation flag

- CP8 Enter lower 64 bits of 95-bit result in X) (complemented if neg.)

I 0032xxxx | Program error exit

[ 0032 ] [ ]