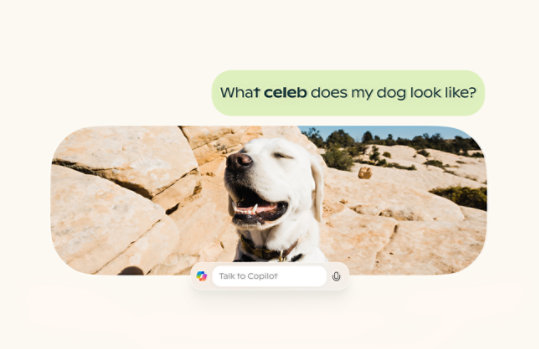

Copilot is your AI companion

Always by your side, ready to support you whenever and wherever you need it.

Speedy DDR2 Controller for FPGAs

The Speedy DDR2 controller is intended as an improvement on the Xilinx MIG controller for Virtex 5 FPGAs. Last published: March 18, 2011.

Important! Selecting a language below will dynamically change the complete page content to that language.

Version:

1.1

Date Published:

7/15/2024

File Name:

SpeedyDDR2ControllerForFPGAs_1_1.msi

File Size:

416.5 KB

The Speedy DDR2 controller is intended as an improvement on the Xilinx MIG controller for Virtex 5 FPGAs. Designed entirely from scratch on the ML505 development board, it achieves better performance at the same clock rate than the MIG controller while consuming comparable resources. The tight timing constraints imposed by high-speed DDR2 clash with the worst-case timing constraint style of FPGA design in a way that presents unique challenges. This paper discusses the primary design problems resulting from that paradox and contrasts approaches to their solutions. Performance then is compared between the Speedy DDR2 controller and the Xilinx MIG controller. The source code has been written to be more readable, maintainable, and modifiable than the MIG design and is freely downloadable from the Web.Supported Operating Systems

Windows 10, Windows 7, Windows 8

- Windows 7, Windows 8, or Windows 10

- Click Download and follow the instructions.

Follow Microsoft